内存真实时钟频率为什么只有一半

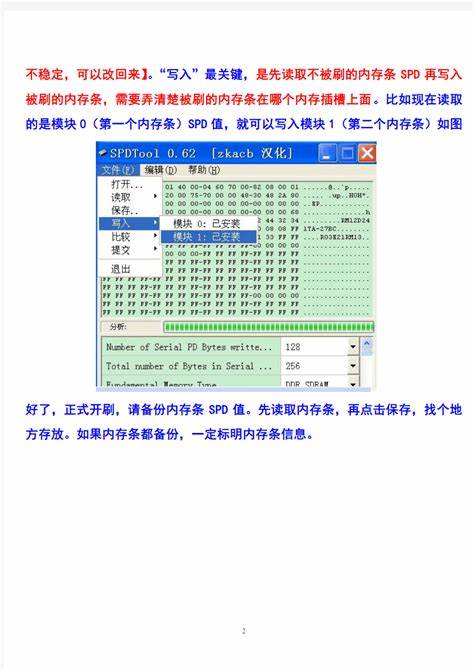

发布时间:2024-06-20 18:09:21从专业角度来说,内存真实时钟频率只有一半是由于 DDR(双倍数据速率)技术和时钟信号传输机制造成的。

DDR技术

DDR 内存使用了一种被称为“双倍数据速率”的技术,它允许每个时钟周期传输两次数据。 这与传统的 SDRAM 内存不同,SDRAM 内存每个时钟周期只传输一次数据。

时钟信号传输机制

DDR 内存利用时钟信号的上升沿和下降沿都传输数据,而不是像 SDRAM 一样只在上升沿传输数据。 这样一来,DDR 内存能够在同一个时钟周期内传输更多数据。

举例说明

假设一个 DDR 内存的时钟频率为 100 MHz,这意味着每个时钟周期的时间为 10 纳秒。 由于 DDR 技术,每个时钟周期可以传输两次数据,因此实际的数据传输速率为 200 MB/s。

总结

由于 DDR 技术和时钟信号传输机制,DDR 内存的真实数据传输速率是其时钟频率的两倍,因此实际数据传输速率是时钟频率的一半。

相关问答

- 内存时钟频率调高行吗2024-06-22

- 内存时钟频率越高越好2024-06-22

- 内存真实时钟频率13332024-06-22

- cpuz显示内存频率只有一半2024-06-22

- 内存真实时钟频率12002024-06-22

- 一个256g内存卡多少钱2024-06-22

- 安装4g内存只有2g可用的解决方法2024-06-22

- 内存超频后进入游戏崩溃2024-06-22

- 运行内存16和12g区别大不大2024-06-22